# NIRSPEC

**UCLA Astrophysics Program**

U.C. Berkeley

W.M. Keck Observatory

#### Maryanne Angliongto

February 19, 1999

# NIRSPEC Electronics Application Note 02.01 NIRSPEC Grounding Scheme Specification

The grounding scheme described in the previous application note (NEAN 02.00) was modified in order to provide a single point ground on the 256 analog system.

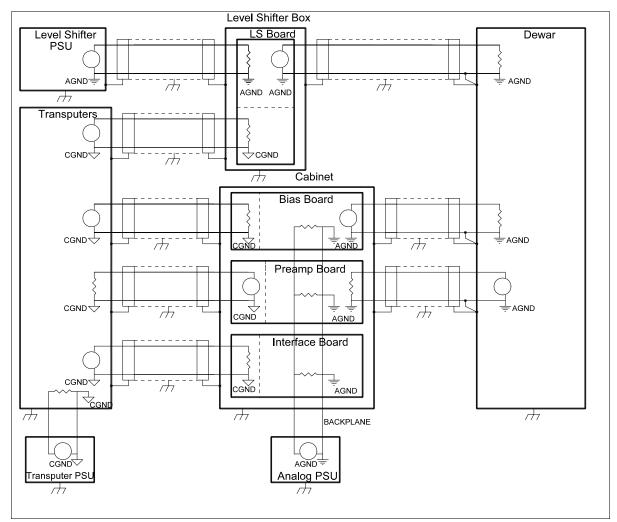

Figure 1. Grounding Scheme for NIRSPEC 256 Analog Electronics

Printed November 28, 2012

## 1. Power Supplies

All NIRSPEC power supplies are of low noise, Faraday double-shielded transformer type. The AC lines to the power supplies are filtered on the primary side and shielded from the system. All the dc voltages are filtered and regulated by an IC regulator. Separate power supplies are used for the analog crates, the transputers, and level shifter box, which ensures isolation between the different electronic circuits.

# 2. Cable Grounding

All power supply cables are twisted with their own returns. The analog signal cables have returns in pins adjacent to their appropriate signals, and have their shields grounded to the cabinet chassis on both ends of the cable. This creates a Faraday shield, surrounding all of the electronics and cables through the dewar wall, the analog crates, and level shifter boxes. The digital signal cables have their shields grounded to chassis and CGND.

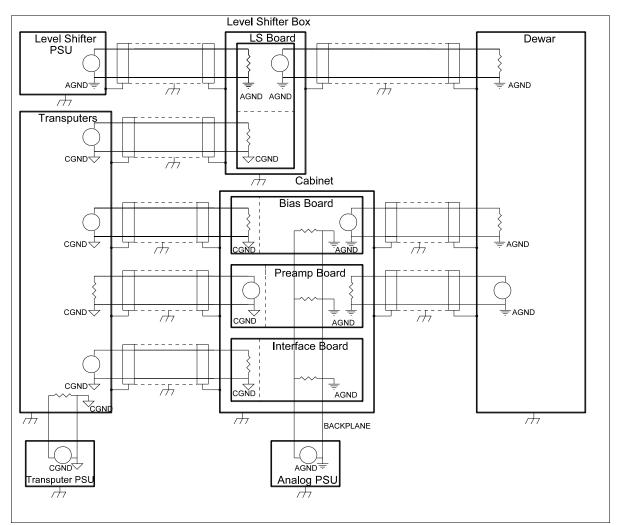

Figure 2. Grounding Scheme for NIRSPEC 1024 Analog Electronics

Printed November 28, 2012

#### 3. Board Grounds

Separated on each board are three types of ground: analog ground (AGND), digital ground (DGND), and computer ground (CGND). Analog and digital ground are separated until they connect at one point on the PC board near the P2 connector. Computer ground is electrically and physically separated from the rest of the board by the ISO150 capacitive isolators. In order to reduce noise pickup from the digital system, the analog boards have grounding clips installed to both sides, so that they are grounded to the analog subrack as closely as possible.

## 4. System Grounds

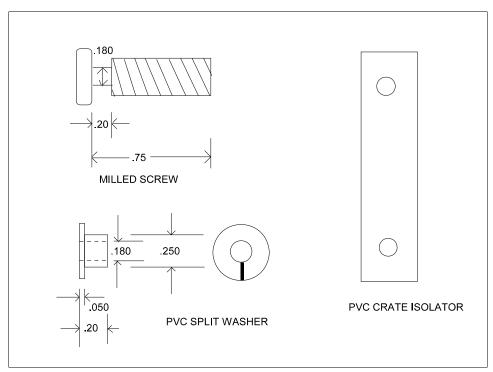

Figure 1 shows an overall picture of the NIRSPEC 256 analog system grounding scheme. All of the returns from the analog boards for each detector are connected at a single point ground, at the dewar wall. The analog board returns are completely isolated from the chassis ground except for this single point ground. These returns are also connected together at the detector PCB. The 256 analog inner crate is isolated from the outer crate by using a PVC strip, as shown in Figure 3.

Figure 2 describes the 1024 analog grounding, which has not been modified to include a single point ground. The 1024 analog board returns are completely isolated from the chassis ground. The 1024 analog crate is isolated from the cabinet by using PVC split washers, as shown in Figure 3.

The 1024 detector head, analog crate, power supply, and level shifter box do not share any ground points with those of the 256 detector array. All connections between the analog subsystems and the transputers are isolated with ISO150s, and do not share any ground connections. The cabinet is connected to earth ground through the AC plugs of each power supply, fan, and Knurr cooling unit. Separate AC units, such as the fans and the Knurr cooling units, receive their AC power directly from the Pulizzi power strip, and are not isolated from the cabinet.

## 5. NIRSPEC Measured Noise Performance

## 5.1 256 Noise Performance

The total noise (system + detector) is evaluated using the difference of two "bias" frames, i.e. two short exposures (0.1 s each) with the detector blanked off from light. This difference frame should exhibit only random noise. Tests gave a standard deviation of 4 data numbers (DN) over the entire frame of 256x256 pixels with only a slight indication of some high frequency residual noise. Since a difference of two frames was used, the standard deviation (or noise) in a single frame is less by the square root of two, i.e. 3 DN. Using the conversion factor of 9.5 microvolts per DN at the detector output gives a total noise of 28.6 microvolts. Similarly, using 4 electrons/DN yields a total readout noise of 12 electrons rms, which is consistent with published data on PICNIC arrays used in others camera systems.

## 5.2 1024 Noise Performance

The total noise (system + detector) is evaluated using the difference of two "bias" frames, i.e. two short exposures (0.25 s each) with the detector blanked off from light. This difference frame should exhibit only random noise. Tests gave a standard deviation of about 20 data numbers (DN) over the entire frame of  $1024 \times 1024$  pixels. This is unusually high and is due largely to the spotted

distribution of bad pixels over the array. When numerous sub-frames of at least 1000 pixels are examined, the standard deviation is much less, typically <14 DN. Since a difference of two frames was used, the standard deviation (or noise) in a single frame is less by the square root of two, i.e. 10 DN. Using the conversion factor of 9.5 microvolts per DN at the detector output gives a total noise of 95 microvolts. Similarly, using 5 electrons/DN yields a total readout noise of 50 electrons rms, which is consistent with test data on this ALADDIN array obtained at NOAO.

Figure 3. Analog and Logic Crate Isolation Components